## EPC C1G2 COMPLIANT UHF RFID TAG WITH POWER HARVESTING AND SPI COMMUNICATION FOR EXTERNAL LOW POWER SENSORS AND ACTUATORS

Check for samples: ROCKY100

## **FEATURES**

- 860MHz-960MHz operation

- EPC C1G2 compliant

- ISO 18000-6 Type C compliant

- 160-bit EPC Bank: Up to 128-bit EPC

- 96-bit TID Bank: Up to 48-bit Serial Number

- Partitioned User Bank: Up to 1008-bit Non Volatile User Data

- Password protected Kill command

- Password protected Access command

- Forward link data rates: 26.7kbps to 128 kbps

- Return link data rates: 40 to 640 kbps

- Return link modulations: FM0 and Miller subcarrier (2, 4, 8)

- Read sensitivity in passive mode without sensors: -14dBm

- High sensitivity in passive mode supplying external sensors: -10dBm (typical case)

- Configurable sensitivity for battery assisted mode: -24dBm (BAP) or -35dBm (EBAP)

- Configurable PSK modulation depth

- Configurable regulated output from 1.2V to 3.0V

- VDD monitor and configurable control for activation of load supply

- Battery switch with 500nA leakage current in open state

- 5 configurable GPIOs

- Configurable SPI master module to control external devices

- SPI slave module to access C1G2 memory space

- · Edge detector for anti-tampering

- Event logger with timestamp

- PWM output generator

- C1G2 related event generator

- Front-end signal bypass

- Extended temperature range: -40°C to +85°C

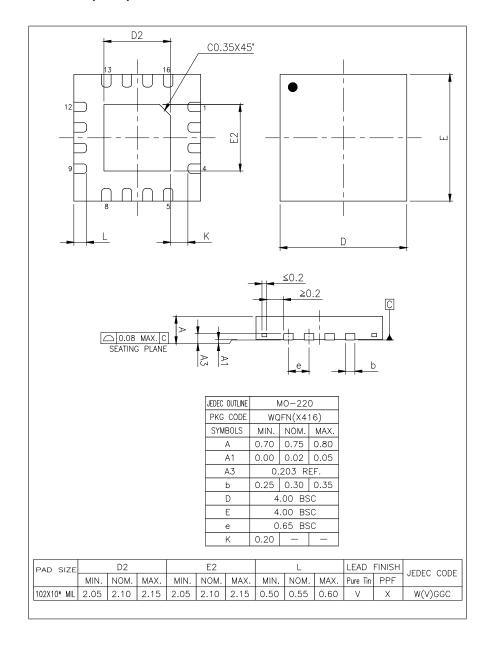

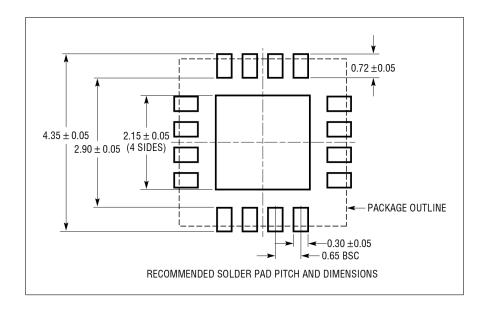

- 4x4mm QFN-16 package

## **APPLICATIONS**

- Wireless identification

- Energy harvesting

- Batteryless wireless sensors/actuators

- TPMS (Tire Pressure Monitoring Systems)

- Cold chain monitoring

- Orientation monitoring

- Fill level monitoring

- Open/close detection

WWW.FARSENS.COM

| CONTENTS                             |    | C1G2 Oscillator                          | 37       |

|--------------------------------------|----|------------------------------------------|----------|

| Features                             | 1  | Operation Mode Registers                 | 38<br>41 |

| i catules                            | •  | PSM Control Registers                    | 42       |

| Applications                         | 1  | GPIO                                     | 44       |

| Davidson Occasional                  | •  | GPIO Registers                           | 48       |

| Device Overview                      | 3  | SPI Master                               | 50       |

| Description                          | 3  | SPI Master Configuration                 | 50       |

| Functional Block Diagram             | 3  | SPI Master Control                       | 53       |

| Terminal Configuration and Functions | 5  | SPI Master Registers                     | 56       |

| Specifications                       | 6  | SPI Slave                                | 58       |

| Absolute Maximum Ratings             | 6  | SPI Slave Configuration                  | 58       |

| Recommended Operating Conditions     | 6  | SPI Slave Control                        | 59       |

| Non Volatile Memory                  | 6  | Edge Detector                            | 61       |

| Electrical Characteristics           | 7  | Signal Monitoring                        | 61       |

| Licotrical characteristics           | ,  | Edge Detection                           | 62       |

| <b>Detailed Description</b>          | 8  | Edge Detector Registers                  | 63       |

| RF                                   | 8  | Example Configuration                    | 64       |

| Power Supply Management              | 9  | Event Logger                             | 65       |

| Power Signals                        | 9  | Event Counter                            | 65       |

| VDD, VSS: Main Power Supply          | 9  | Log Time Counter                         | 66       |

| VBAT: Auxiliary Power Supply         | 9  | Event Stamp                              | 66       |

| VREGL: Regulated Output              | 11 | Autostart                                | 67       |

| GLOAD: Switched Ground               | 16 | Event Logger Registers                   | 68       |

| VDD Monitor: Load Switching          | 17 | PWM                                      | 72       |

| Memory Space Definition              | 18 | PWM Registers                            | 73       |

| EPC C1G2                             | 24 | Configuration Control                    | 75       |

| Reserved Memory Bank                 | 24 | Configuration Control Registers          | 76       |

| EPC Memory Bank                      | 27 | Reboot                                   | 81       |

| TID Memory Bank                      | 30 | Reboot Register                          | 81       |

| User Memory Bank                     | 32 | Watchdog Timer                           | 82       |

| Peripheral Base Address              | 33 | Watchdog Timer Registers                 | 82       |

| Peripheral Base Address Register     | 33 |                                          |          |

| SPI Base Address                     | 34 | Applications, Implementation, and Layout | 83       |

| SPI Base Address Register            | 34 | Application Information                  | 83       |

| Operation Mode                       | 35 |                                          |          |

| ASK Mode                             | 35 | Mechanical, Packaging, and Orderable     |          |

| BAP Mode                             | 36 | Information                              | 84       |

| PSK Mode                             | 36 | References                               | 84       |

| RNG Mode                             | 37 | Packaging                                | 85       |

## **DEVICE OVERVIEW**

#### **DESCRIPTION**

ROCKY100 is an EPC Class-1 Generation-2 (C1G2) RFID tag IC which is compliant with ISO/IEC 18000-6 Type C. The chip offers advanced capabilities leading to a performance beyond that of standard RFID tags by including sensor measurements and actuator control.

The IC operates in a fully passive mode harvesting energy from the RF beam emitted by the reader. With an external power source, the IC can operate in Battery Assisted Passive (BAP) mode with enhanced communication range.

ROCKY100 includes a non volatile memory to store unique identifiers and passwords for item identification and data protection operations. The memory includes an up to 128-bit length *Electronic Product Code* (EPC) supporting EPCGlobal Tag Data Standards. The memory also includes a 96-bit length *Tag IDentifier* (TID) supporting ISO/IEC 15963 class-identification. Separate 32-bit length Kill and Access passwords are also included supporting protected kill and data access operations.

Additionally, ROCKY100 supports extending the classic functionality of C1G2 tags by attaching an external system to the IC. ROCKY100 includes the necessary power supply management circuitry to supply external sensors or actuators with the energy harvested from the RF field. It also includes configurable GPIOs to communicate with the external device, trigger operations and retrieve data prior to backscattering the obtained answer to the reader. All the operations are commanded by the reader using standard memory access commands making the system directly compatible with any standard C1G2 RFID system.

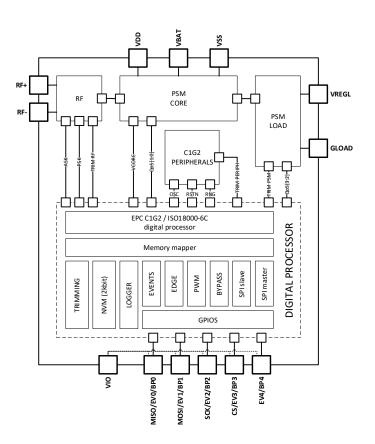

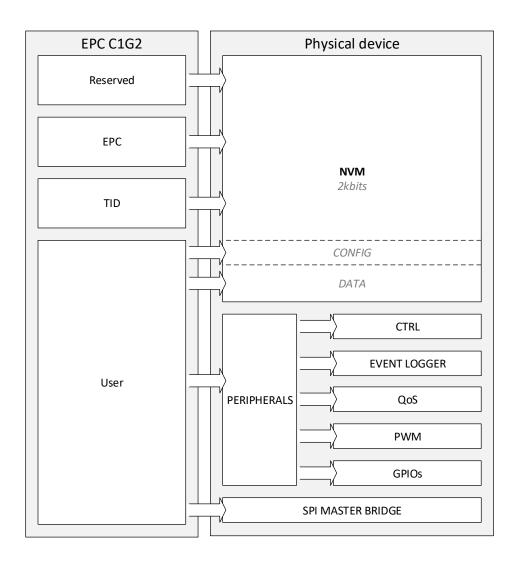

#### **FUNCTIONAL BLOCK DIAGRAM**

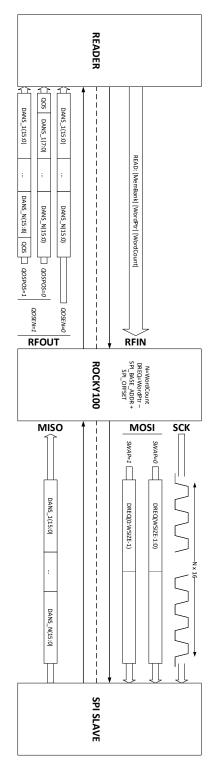

The functional block diagram of ROCKY100 is shown in figure 1. The RF front-end provides the core RFID functionality, including energy harvesting from the RF field, demodulation of *Amplitude Shift Keying* (ASK) symbols in the forward link and *Phase Shift Keying* (PSK) modulation of the impedance of the IC to backscatter data through the reverse link. The device allows configuring the ASK sensitivity and the PSK modulation depth.

The harvested energy is managed by a power supply management unit. This unit includes several low dropout regulators to provide stable supply voltages for internal circuitry and external devices. Several voltage monitors are included to ensure proper start-up of the system.

Additionally, the device can be powered up using an external battery. A dedicated pin allows connecting such a battery with low drain current and activating the use of the battery upon request.

A configurable LDO regulator is included for the load power supply generation. Moreover, the supply and ground of the load can be connected and disconnected automatically to ensure proper supply during the operation of the load by means of analog switches and a voltage monitor.

An application specific digital processor handles the ISO/IEC 18000-6 Type C air protocol managing the non volatile memory according to the standard. The digital processor controls several devices to add functionality to ROCKY100: 5 GPIOs, an SPI module (master/slave), an event generator, an edge detector, an event logger, a PWM generator and a signal bypass module.

The GPIOs can be used either as general purpose input/output, or can be configured to be controlled by the other peripherals.

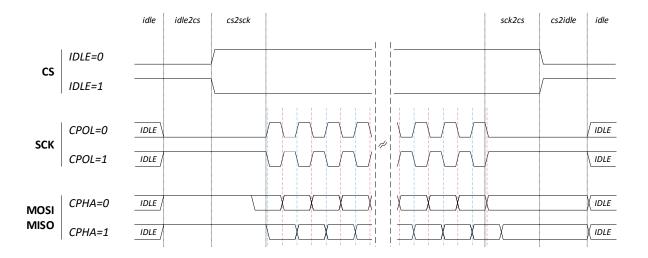

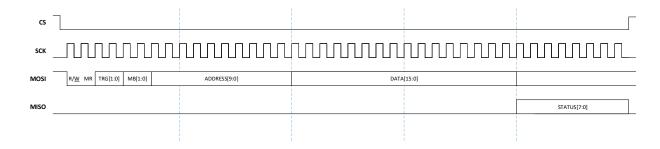

The SPI module can be configured as a master or a slave device, and it can be used to control and retrieve data from external digital systems. In master mode, the operation of the SPI is commanded through standard memory access commands included in the ISO/IEC 18000-6 Type C standard.

Figure 1: Block diagram of ROCKY100

The event generator allows notifying an external system when certain C1G2 relative event occurs. This functionality can be used to wake up external devices in a controlled way using UHF RFID readers.

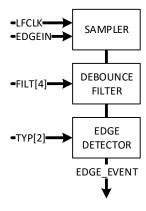

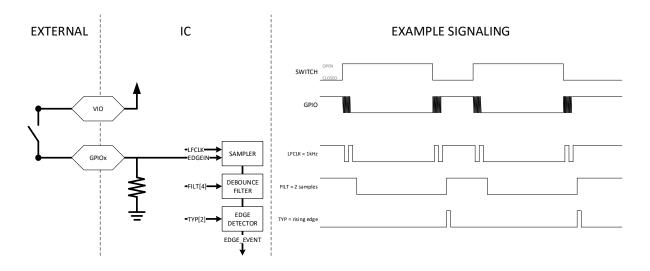

The edge detector allows detecting state changes in input signals and adds anti-debounce capabilities.

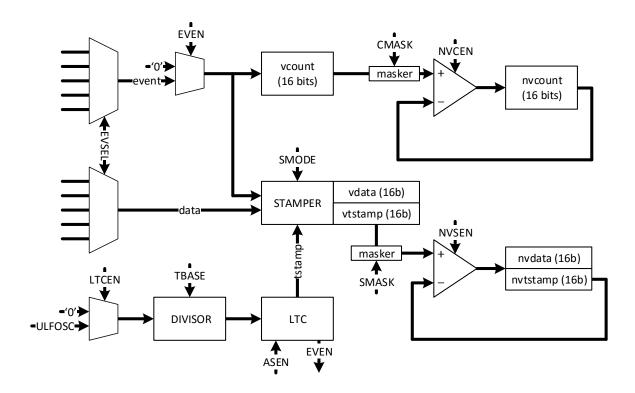

The event logger keeps track of time and automatically logs timestamps and associated data values upon certain events, such as edge detection.

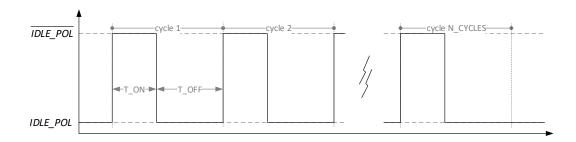

The PWM generator can be configured to generate a specific PWM signaling upon request.

The signal bypass module allows bypassing some of the internal signals provided by the RF front-end directly to the GPIOs. This mode is useful to use the physical layer of the EPC C1G2 standard and customize the upper layers. Note that in this case, the capability of communicating with commercial readers is no more controlled by the digital processor. The external device is responsible for fulfilling or not the communication standard.

Additionally, a configuration blockage system is implemented in order to allow blocking some of the configurable parameters.

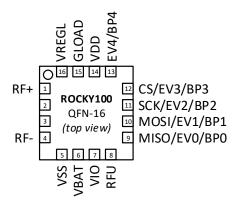

# **TERMINAL CONFIGURATION AND FUNCTIONS**

Figure 2: Pin diagram for QFN-16.

| PIN          |     | TYPE  | DESCRIPTION                                         |  |  |  |  |  |

|--------------|-----|-------|-----------------------------------------------------|--|--|--|--|--|

| NAME         | NO. | 1176  | DESCRIPTION                                         |  |  |  |  |  |

| RF           |     |       |                                                     |  |  |  |  |  |

| RF+          | 1   | RF    | Positive input of differential RF signal            |  |  |  |  |  |

| RF-          | 4   | RF    | Negative input of differential RF signal            |  |  |  |  |  |

| Power supply |     |       |                                                     |  |  |  |  |  |

| VDD          | 14  | Power | Supply voltage of the tag                           |  |  |  |  |  |

| VSS          | 5   | Power | Ground of the tag                                   |  |  |  |  |  |

| VBAT         | 6   | Power | Battery supply voltage                              |  |  |  |  |  |

| VREGL        | 16  | Power | Regulated load supply output                        |  |  |  |  |  |

| GLOAD        | 15  | Power | Switched ground of the load                         |  |  |  |  |  |

| Digital I/O  |     |       |                                                     |  |  |  |  |  |

| VIO          | 7   | Power | Power supply for the digital I/O pins               |  |  |  |  |  |

| RFU          | 8   | Input | Reserved for future use. Connect to VSS.            |  |  |  |  |  |

| MISO/EV0/BP0 | 9   | I/O   | SPI master input line / Event pin 0 / Bypass pin 0  |  |  |  |  |  |

| MOSI/EV1/BP1 | 10  | I/O   | SPI master output line / Event pin 1 / Bypass pin 1 |  |  |  |  |  |

| SCK/EV2/BP2  | 11  | I/O   | SPI clock line / Event pin 2 / Bypass pin 2         |  |  |  |  |  |

| CS/EV3/BP3   | 12  | I/O   | SPI chip select line / Event pin 3 / Bypass pin 3   |  |  |  |  |  |

| EV4/BP4      | 13  | I/O   | Event pin 4 / Bypass pin 4                          |  |  |  |  |  |

# **SPECIFICATIONS**

# **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL               | PARAMETER                        | MIN  | МАХ     | UNIT |

|----------------------|----------------------------------|------|---------|------|

| $P_{RF}$             | RF input power                   |      | 20      | dBm  |

| VDD                  | Supply voltage                   | -0.5 | 5.0     | V    |

| VIO                  | IO supply voltage                | -0.5 | 5.0     | V    |

| V <sub>iO</sub>      | Input voltage at any digital pin | -0.5 | VIO+0.5 | V    |

| T <sub>storage</sub> | Storage temperature              | -40  | 125     | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL       | PARAMETER                | MIN | TYP | MAX | UNIT |  |  |  |  |

|--------------|--------------------------|-----|-----|-----|------|--|--|--|--|

| RF           |                          |     |     |     |      |  |  |  |  |

| $P_{RF}$     | RF input power           |     |     | 10  | dBm  |  |  |  |  |

| POWER SUPPLY |                          |     |     |     |      |  |  |  |  |

| VDD          | Supply voltage           | 1.4 |     | 3.0 | V    |  |  |  |  |

| VBAT         | Auxiliary supply voltage | 1.4 |     | 3.0 | V    |  |  |  |  |

| VIO          | IO supply voltage        | 1.4 |     | 3.0 | V    |  |  |  |  |

| TEMPERATURE  |                          |     |     |     |      |  |  |  |  |

| Toperation   | Operation temperature    | -40 |     | 85  | °C   |  |  |  |  |

# **NON VOLATILE MEMORY**

| PARAMETER                    | MIN             | UNIT   |

|------------------------------|-----------------|--------|

| Data retention @85°C         | 10              | years  |

| Number of erase/write cycles | 10 <sup>4</sup> | cycles |

# **ELECTRICAL CHARACTERISTICS**

| SYMBOL                 | PARA                 | METER                 | MIN             | TYP             | MAX                 | UNIT    |

|------------------------|----------------------|-----------------------|-----------------|-----------------|---------------------|---------|

| RF                     |                      |                       |                 |                 |                     |         |

|                        | RF sensitivity ID    |                       |                 | -14             |                     | dBm     |

| DE                     | RF sensitivity Typic | cal Load <sup>1</sup> |                 | -10             |                     | dBm     |

| RF <sub>SENS</sub>     | RF sensitivity BAP   |                       |                 | -24             |                     | dBm     |

|                        | RF sensitivity Enha  | anced BAP             |                 | -35             |                     | dBm     |

|                        | Input impedance      | QF16@868MHz           |                 | 64 - 469j       |                     | Ω       |

| Z <sub>IN</sub>        | ID                   | QF16@915MHz           |                 | 51 - 460j       |                     | Ω       |

| <i>7</i> <sub>1N</sub> | Input impedance      | QF16@868MHz           |                 | 80 - 493j       |                     | Ω       |

| — <i>IIV</i>           | Typical Load         | QF16@915MHz           |                 | 52 - 479j       |                     | Ω       |

|                        | Input impedance      | QF16@868MHz           |                 | 35 - 451j       |                     | Ω       |

|                        | BAP                  | QF16@915MHz           |                 | 14 - 456j       |                     | Ω       |

| TAG POWER              | RSUPPLY              |                       |                 |                 |                     |         |

| VDD                    | Supply voltage       |                       | 1.4             | $V_L$           | V <sub>L</sub> +0.2 | V       |

| $V_L$                  | Limitation voltage   |                       |                 | 3.2             |                     | V       |

|                        |                      | Base                  |                 | 7               |                     | $\mu$ A |

| ,                      | Supply current       | Enhanced BAP          |                 | +2              |                     | $\mu$ A |

| $I_{DD}$               | Cappiy current       | VDD Monitor           |                 | +1              |                     | $\mu$ A |

|                        |                      | VREGL LDO             |                 | +0.5            |                     | $\mu$ A |

| I <sub>BAT</sub>       | Battery leakage cu   | rrent <sup>2</sup>    |                 | 0.5             |                     | $\mu$ A |

| LOAD POW               | ER SUPPLY            |                       |                 |                 |                     |         |

| VREGL                  | Regulated load su    | oply output           | 1.2             |                 | 3.0                 | V       |

| RES <sub>VREGL</sub>   | Resolution of VRE    | GL voltage            |                 |                 | 3                   | mV      |

| ACC <sub>VREGL</sub>   | Accuracy of VREG     | L voltage             |                 | ±5              |                     | %       |

| I <sub>VREGL</sub>     | Driving strength of  | VREGL                 | 0               |                 | 5                   | mA      |

| DIGITAL I/O            |                      |                       | <u>'</u>        |                 |                     |         |

| VIO                    | IO supply voltage    |                       | 1.4             |                 | 3.6                 | V       |

| V <sub>ih</sub>        | Input high voltage   |                       | 0.7×VIO         |                 | <i>VIO</i> +0.5     | V       |

| $V_{il}$               | Input low voltage    | -0.5                  |                 | 0.3× <i>VIO</i> | V                   |         |

| I <sub>Ikg</sub>       | Input leakage curre  |                       |                 | ±1              | $\mu$ A             |         |

| V <sub>oh</sub>        | Output high voltage  | e                     | 0.8× <i>VIO</i> |                 |                     | V       |

| $V_{ol}$               | Output low voltage   |                       |                 |                 | 0.2× <i>VIO</i>     | V       |

| I <sub>drive</sub>     | Output driving stre  | ngth <sup>1</sup>     |                 |                 | 1                   | mA      |

$<sup>^{1}</sup>$  Typical Load of 5  $\mu A$  at 1.8V  $^{2}$  With BATSW in open state. When BATSW is closed,  $I_{BAT}=I_{DD}.$

## **DETAILED DESCRIPTION**

## **RF**

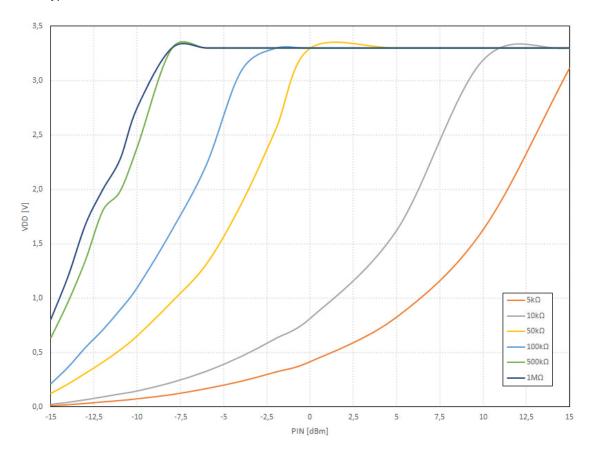

The RF block can harvest energy from the incoming RF signal in the antenna. It has an integrated voltage multiplier in order to escalate the small AC voltage at the input of the antenna to a higher DC voltage. The voltage available in VDD will depend on the incoming RF energy and the load connected to the tag. The following figure shows the typical behavior of ROCKY100 for different load conditions.

Figure 3: VDD (V) vs.  $P_{IN}$  (dBm) for different  $R_{LOAD}$ .

The RF block includes a voltage limiter to make sure that the voltage available at VDD never exceeds the limits of the technology. An external load can be connected to VDD to power external devices.

A battery can be connected to VDD so that the RF block is only used for passive communication. In this configuration, both the supply current of the RFID circuitry and the load are powered by the battery. Thus, the sensitivity of the tag is improved to the communication sensitivity. Moreover, in this configuration the high sensitivity demodulator can be enabled enhancing the communication sensitivity in expenses of increasing slightly the current consumption.

#### POWER SUPPLY MANAGEMENT

ROCKY100 includes a complete PSM for proper operation. In the one hand, this system manages the incoming energy from the RF front-end. This energy is delivered both to the internal circuitry and to the load of the device.

In the other hand, the system also controls a battery power input. If a power source is connected to this input, depending on the active configuration, the PSM will connect this input to the supply voltage of the device or keep it disconnected with a low leakage current.

Moreover, the PSM includes a smart control system to power up the external loads. For instance, a configurable LDO regulator is used to provide a stable voltage to the external load. Additionally, an analog switch can be used to connect the ground of the load to VSS only under certain circumstances. Finally, a voltage monitor is included to activate the LDO regulator and the ground switch when the supply voltage is within a configurable range.

#### **POWER SIGNALS**

For a clear understanding of the following description, a brief summary of the available power signals is presented:

- VDD: positive supply voltage of the device. The positive voltage generated in the RF energy harvester is delivered to this net.

- VSS: negative supply voltage of the device. The negative voltage generated in the RF energy harvester is delivered to this net.

- VBAT: battery input. This power signal can be connected to VDD changing the configuration bits.

- VREGL: configurable LDO regulator output for external loads. This block is powered from VDD.

- GLOAD: switched ground for external loads. The switching behavior is controlled with configuration bits.

## **VDD, VSS: MAIN POWER SUPPLY**

The power nets VDD and VSS are the main power supply of ROCKY100. All internal electronics of the device drain their operating current from this source.

The RF energy harvesting module injects small amounts of current through a voltage multiplier to the supply capacitor connected to these nets. Thus, when the device is in presence of an RF emitter, some DC voltage will appear in VDD. As detailed in figure 3, the generated voltage depends on the input power in the RF pins and the average power consumption of the device.

The internal electronics of ROCKY100 are designed taking into account the nature of this power supply. However, even if it is possible to connect an external load to VDD, it is not recommended to do so. These loads have to comply several restrictions. First of all, the average power consumption of the external device must be low enough to be powered by the harvested energy. Additionally, as no regulation is applied to the main supply signals, the load has to support a variable supply voltage. Finally, the load can not have high current consumption peaks, as this would make the system oscillate during start-up. There are not many sensors nor actuators fulfilling all these conditions.

In order to make ROCKY100 an easy to use device, the PSM provides a regulated voltage supply to the external load. Moreover, the supply and ground of this load are switched off during start-up of the tag, so that they are connected only after monitoring a high enough supply voltage to assure a stable start-up.

#### **VBAT: AUXILIARY POWER SUPPLY**

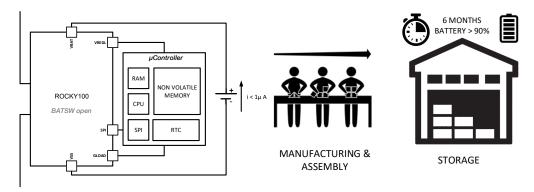

ROCKY100 can be used in BAP mode. This means that a battery can be used to enhance the characteristics of the device. However, in many applications it may be of interest to connect the battery without starting to drain

energy from it, and activate the current drain later on. This functionality allows manufacturing and assembling the final product with the battery, store it for some time without draining out the battery, and activate the use of the device wirelessly when required.

For that purpose the dedicated battery pin VBAT is included in ROCKY100. This net is not directly connected to VDD, but through a configurable analog switch. The state of the switch can be changed by means of the digital interfaces of the device, such as the RF or SPI interface.

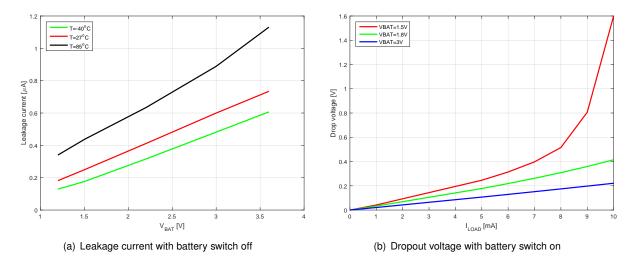

The following graphs show the detailed characteristics of the VBAT switch.

Figure 4: Detailed characteristics of VBAT switch.

The next image shows an example usage of this functionality. First, a ROCKY100 powered BAP data logger is manufactured and assembled with a battery. The device is stored in a warehouse for 6 months. Then the product is taken to the field and the battery is activated via RF interface. In this step, the activation is done with passive characteristic as the battery has not been activated yet. Then, the device is used during 1 year logging sensor information with BAP characteristics.

(a) BAP datalogger in idle mode ( $i_{DD} < 1\mu A$ )

(b) BAP datalogger in active mode ( $\it i_{DD} > 10 \mu A$ )

Figure 5: BAP datalogger example.

## **VREGL: REGULATED OUTPUT**

ROCKY100 includes a low dropout regulator in the PSM block. The output voltage of this regulator can be configured inside the 1.2V-3.0V range. An integrated trimming resistor is used to configure the feedback value of the regulator. The output voltage of VREGL can be set modifying the TRIM\_PSM register.

This regulator can be enabled and disabled automatically commanded by VDD MONITOR or can be manually controlled by the user (refer to section PSM in page 41 for further details). Make sure the VDD monitor is configured correctly prior to using the VREGL output in automatic switching mode.

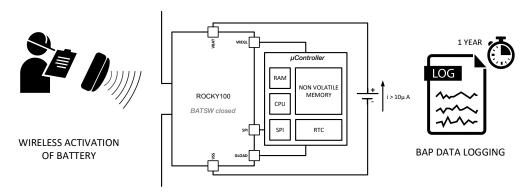

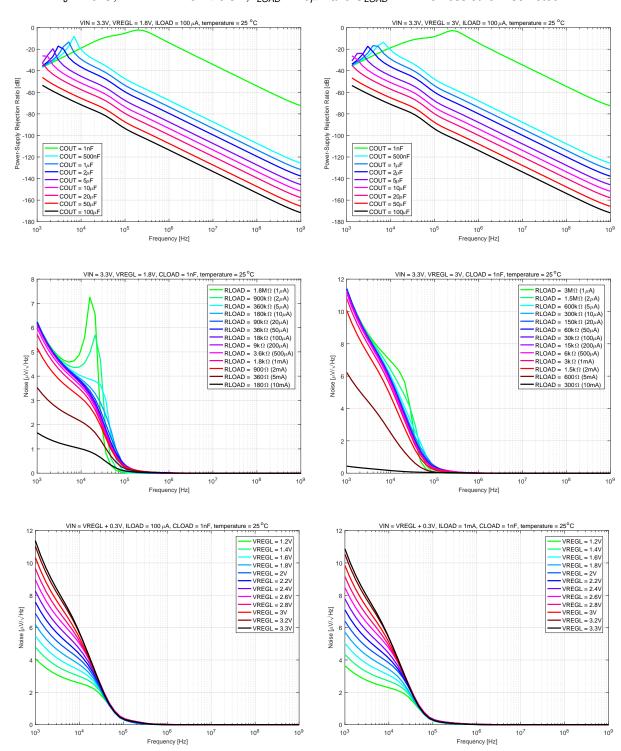

The following graphs show the typical characteristics of the VREGL LDO regulator.

WWW.FARSENS.CO

Figure 6: Typical characteristics of VREGL LDO regulator. (Part 1)

$T_J = 25^{\circ} C$ , VDD = VREGL + 0.3 V,  $I_{LOAD} = 10 \mu A$  and  $C_{LOAD} = 1 nF$  unless otherwise noted.

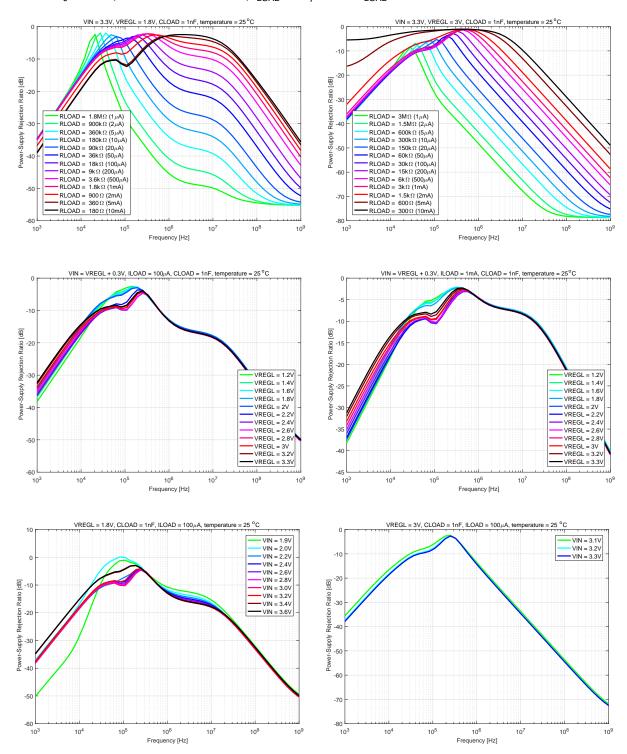

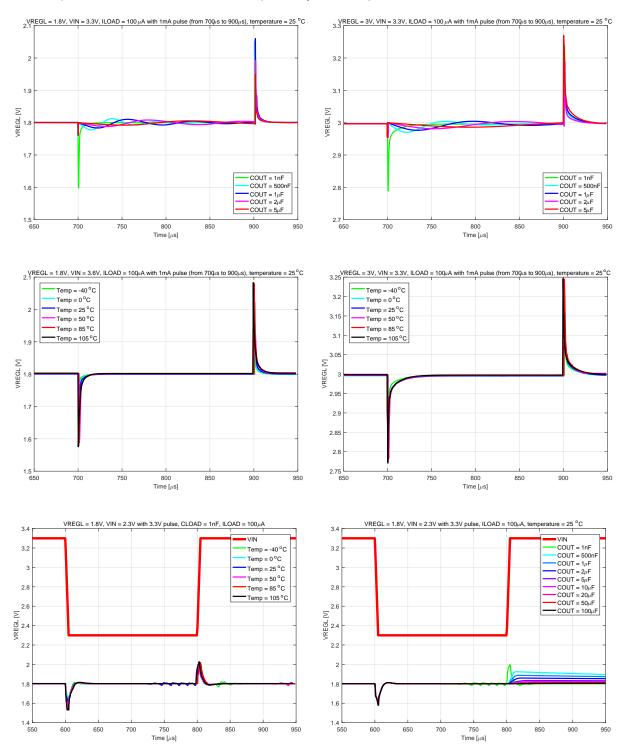

Figure 7: Typical characteristics of VREGL LDO regulator. (Part 2)

WWW.FARSENS.COM

Figure 8: Typical characteristics of VREGL LDO regulator. (Part 3)

$T_J = 25^{\circ} C$ , VDD = VREGL + 0.3 V,  $I_{LOAD} = 10 \mu A$  and  $C_{LOAD} = 1 nF$  unless otherwise noted.

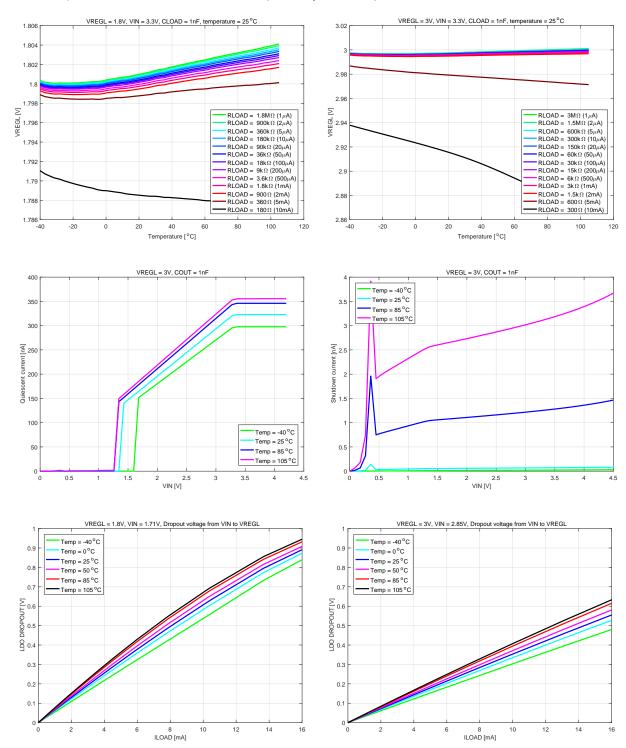

Figure 9: Typical characteristics of VREGL LDO regulator. (Part 4)

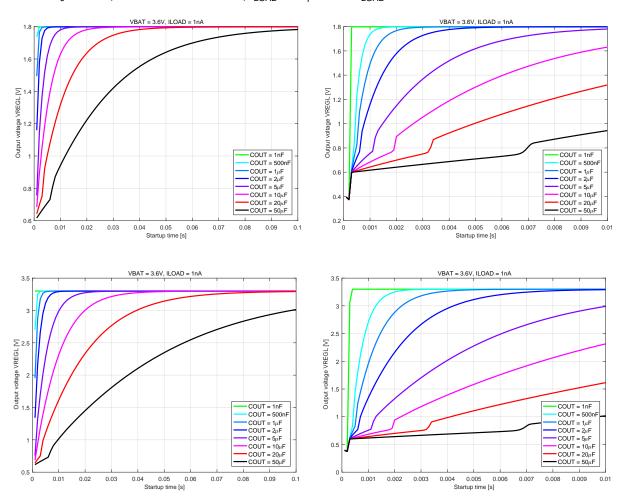

Figure 10: Typical characteristics of VREGL LDO regulator. (Part 5)

## **GLOAD: SWITCHED GROUND**

ROCKY100 includes a dedicated pin to connect the ground of the load. This net is not directly connected to VSS but through an analog switch. This switch is kept open during the start-up of the device, so that no current drain is produced from the sensor.

This switch can be open and closed automatically commanded by VDD MONITOR or can be manually controlled by the user (refer to section PSM in page 41 for further details). Make sure the VDD monitor is configured correctly prior to connecting any load in automatic switching mode.

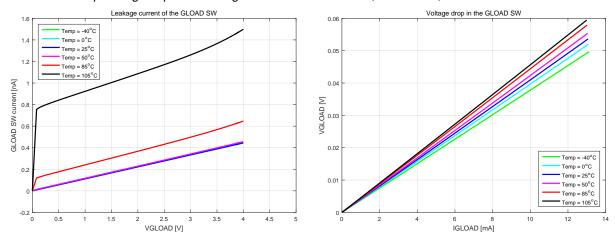

The following graphs show the detailed characteristics of the GLOAD switch.

Over the operating temperature range of  $T = -40 \,^{\circ}$  C to  $85 \,^{\circ}$  C, VDD = 3V, unless otherwise noted.

Figure 11: Detailed characteristics of GLOAD switch.

### **VDD MONITOR: LOAD SWITCHING**

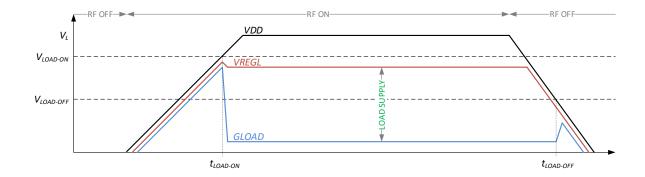

In order to avoid start-up oscillation, the load should be connected only after enough energy has been harvested to support its initialization. For this purpose, the VDD voltage is monitored and compared to two threshold values VLOADON and VLOADOFF. Once VDD is over VLOADON, the output of VREGL is enabled and the GLOAD switch is closed if automatic control is enabled.

If the VDD voltage drops below VLOADOFF, the output of VREGL is disabled and the GLOAD switched is open. This way, unexpected current rushes of the load in the out of specification regions are avoided.

Integrated trimming resistors are used to configure the feedback values of the VDD monitor. The threshold voltages VLOADON and VLOADOFF can be set modifying the TRIM\_PSM register.

If the VDD monitor feature is not required in a specific application, it can be disabled in order to reduce the current consumption of the device.

Figure 12: Functional diagram of VDD MONITOR and switched load supply.

#### **MEMORY SPACE DEFINITION**

The EPC Class-1 Generation-2 protocol defines a unique memory space divided in four banks: Reserved memory, EPC memory, TID memory and User memory. However, unlike traditional tags, this IC includes different physical devices which have to be addressed from the reader. Thus, a memory map table has been defined in order to be able to access any of the physical devices from the unique memory space defined in the communication standard.

Figure 13: Memory space definition.

Figure 13 shows the generic structure used to map the EPC C1G2 memory space to the different devices included in the IC. As the Reserved, EPC and TID memory banks have to follow a standard-defined structure for its contents, the User memory bank is used to access the additional resources of the tag.

Some addresses of the User memory are mapped to the non volatile memory. The non volatile content from

the user memory is divided in two types of data: configuration and user data. The configuration portion of the non volatile memory is further divided into blocks of 16 consecutive registers ranging from addresses 0x00X0 to 0x00XF. ROCKY100 contains three of such configuration blocks, labeled from ConfBlock0 to ConfBlock2. Other addresses of the User memory are mapped to the internal peripherals of the IC: control, event logger, QoS, PWM and GPIOs. Some of those peripherals just provide information and their corresponding registers can only be read. Others are used to trigger actions, and can only be written. And the rest can be both read and written. Take care of making good use of each register in order to obtain the correct functionality.

Finally, the remaining addresses of the User memory are mapped to the SPI master bridge. The reason of mapping all remaining addresses to this device is that the received register address is used to send data through the MOSI pin.

The peripheral base address and the SPI master bridge base address are set to default values on manufacturing. But these values can be changed in order to prevent the loss of some functionality if the reader used to control the IC has limited addressing capabilities.

The memory map of the internal registers is shown in tables 1 to 4. The addressing of the registers consists on a memory bank identifier plus the physical address inside this memory bank.

A detailed description of each register can be found in the following sections.

Table 1: Memory map (part 1)

| AD  | DRESS           | REGISTER              | DESCRIPTION                                  |

|-----|-----------------|-----------------------|----------------------------------------------|

| RE  | SERVED          | memory bank (non-vo   | platile)                                     |

|     | 0x00            | KILL_PWD_H            | Kill password 16 MSB                         |

|     | 0x01            | KILL_PWD_L            | Kill password 16 LSB                         |

|     | 0x02            | ACCESS_PWD_H          | Access password 16 MSB                       |

|     | 0x03            | ACCESS_PWD_L          | Access password 16 LSB                       |

|     | 0x04            | SILICON_REV           | Tag hardware revision identifier             |

|     | 0x05            | CURRENT_PBA           | Peripheral Base Address being used by the IC |

|     | 0x06            | CURRENT_SBA           | SPI Base Address being used by the IC        |

| EF  | <b>PC</b> memor | y bank (non-volatile) |                                              |

|     | 0x00            | STORED_CRC            | Stored CRC value                             |

|     | 0x01            | STORED_PC             | Protocol-control word                        |

|     | 0x02            | EPC_0                 | Word 0 (MSB) of the EPC                      |

|     | 0x03            | EPC_1                 | Word 1 of the EPC                            |

|     | 0x04            | EPC_2                 | Word 2 of the EPC                            |

|     | 0x05            | EPC_3                 | Word 3 of the EPC                            |

|     | 0x06            | EPC_4                 | Word 4 of the EPC                            |

|     | 0x07            | EPC_5                 | Word 5 of the EPC                            |

|     | 0x08            | EPC_6                 | Word 6 of the EPC                            |

|     | 0x09            | EPC_7                 | Word 7 (LSB) of the EPC                      |

| TIL | <b>D</b> memory | bank (non-volatile)   |                                              |

|     | 0x00            | SHORT_TAG_ID_0        | First word of the short tag identification   |

|     | 0x01            | SHORT_TAG_ID_1        | Second word of the short tag identification  |

|     | 0x02            | XTID                  | Extended tag identification header           |

|     | 0x03            | SN_SEG_0              | Bits 47-32 of the Serial Number Segment      |

|     | 0x04            | SN_SEG_1              | Bits 31-16 of the Serial Number Segment      |

|     | 0x05            | SN SEG 2              | Bits 15-0 of the Serial Number Segment       |

Table 2: Memory map (part 2).

| ADDRESS  | REGISTER                  | DESCRIPTION                              |  |  |  |  |  |  |

|----------|---------------------------|------------------------------------------|--|--|--|--|--|--|

| USER mem | ory bank - ConfBlock 0 (i | non-volatile)                            |  |  |  |  |  |  |

| 0x00     | OPMODE_CTL_NV             | Operation mode non-volatile control word |  |  |  |  |  |  |

| 0x01     | TRIM_C1G2OSC              | Trimming bits for C1G2 oscillator        |  |  |  |  |  |  |

| 0x02     | PSM_CTL                   | Trimming bits for VLOAD domain (part 2)  |  |  |  |  |  |  |

| 0x03     | TRIM_VLON                 | Trimming bits for VLOAD ON monitor       |  |  |  |  |  |  |

| 0x04     | TRIM_VLOFF                | Trimming bits for VLOAD OFF monitor      |  |  |  |  |  |  |

| 0x05     | TRIM_VREGL                | Trimming bits for VREGL feedback         |  |  |  |  |  |  |

| 0x06     | GPIO0_CTL                 | GPIO0 control word                       |  |  |  |  |  |  |

| 0x07     | GPIO1_CTL                 | GPIO1 control word                       |  |  |  |  |  |  |

| 0x08     | GPIO2_CTL                 | GPIO2 control word                       |  |  |  |  |  |  |

| 0x09     | GPIO3_CTL                 | GPIO3 control word                       |  |  |  |  |  |  |

| 0x0A     | GPIO4_CTL                 | GPIO4 control word                       |  |  |  |  |  |  |

| 0x0B     | SPI_MASTER_CTL            | SPI master control word                  |  |  |  |  |  |  |

| 0x0C     | QOS_CTL                   | QoS control word                         |  |  |  |  |  |  |

| 0x0D     | PER_BASE_ADDR             | Peripheral partition base address        |  |  |  |  |  |  |

| 0x0E     | SPI_BASE_ADDR             | SPI partition base address               |  |  |  |  |  |  |

| 0x0F     | CFG_LOCK_0                | Configuration block word 0               |  |  |  |  |  |  |

Table 3: Memory map (part 3).

| ADDRESS          | REGISTER                                     | DESCRIPTION                                       |  |  |  |  |  |  |  |

|------------------|----------------------------------------------|---------------------------------------------------|--|--|--|--|--|--|--|

| USER mem         | USER memory bank - ConfBlock1 (non-volatile) |                                                   |  |  |  |  |  |  |  |

| 0x10             | CFG_READ_1                                   | Peripheral configuration read block word 1        |  |  |  |  |  |  |  |

| 0x11             | TRIM_ULFOSC                                  | Trimming bits for ULF oscillator                  |  |  |  |  |  |  |  |

| 0x12<br><br>0x19 | RFU                                          | Reserved for future use                           |  |  |  |  |  |  |  |

| 0x1A             | WDT_CTL                                      | Watchdog control word                             |  |  |  |  |  |  |  |

| 0x1B             | EDGE_CTL                                     | Edge module control word                          |  |  |  |  |  |  |  |

| 0x1C             | SPI_OFFSET_H                                 | Most significant bits of the SPI offset register  |  |  |  |  |  |  |  |

| 0x1D             | SPI_OFFSET_L                                 | Least significant bits of the SPI offset register |  |  |  |  |  |  |  |

| 0x1E             | LTC_CTL                                      | Log Time Counter control word                     |  |  |  |  |  |  |  |

| 0x1F             | CFG_LOCK_1                                   | Configuration block word 1                        |  |  |  |  |  |  |  |

Table 4: Memory map (part 4).

| ADDRESS REGISTER |                          | DESCRIPTION                                                            |  |  |  |  |  |  |  |

|------------------|--------------------------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

| USER mem         | ory bank - ConfBlock2 (n | on-volatile)                                                           |  |  |  |  |  |  |  |

| 0x20             | CFG_READ_2               | Peripheral configuration read block word 2                             |  |  |  |  |  |  |  |

| 0x21             | LOG_CTL                  | Event logger module control word                                       |  |  |  |  |  |  |  |

| 0x22             | LOG_NVCOUNT              | Event logger non-volatile count                                        |  |  |  |  |  |  |  |

| 0x23             | LOG_NVTSTAMP             | Event logger non-volatile time-stamp                                   |  |  |  |  |  |  |  |

| 0x24             | LOG_NVDATA               | Event logger non-volatile data                                         |  |  |  |  |  |  |  |

| 0x25             | PWM_CTL                  | PWM control word                                                       |  |  |  |  |  |  |  |

| 0x26<br><br>0x2E | RFU                      | Reserved for future use                                                |  |  |  |  |  |  |  |

| 0x2F             | CFG_LOCK_2               | Configuration block word 2                                             |  |  |  |  |  |  |  |

| USER mem         | ory bank - User data (no | n-volatile)                                                            |  |  |  |  |  |  |  |

| 0x30<br><br>0x6E | USER_DATA                | Free memory for user data (Up to 1.008 bits, depending on CURRENT_PBA) |  |  |  |  |  |  |  |

Table 5: Memory map (part 5).

| ADDRESS  | REGISTER                 | DESCRIPTION                                          |  |  |  |  |

|----------|--------------------------|------------------------------------------------------|--|--|--|--|

| USER mem | ory bank - Peripheral pa | rtition (volatile, referred to CURRENT_PBA)          |  |  |  |  |

| 0x00     | REBOOT                   | Soft reboot trigger                                  |  |  |  |  |

| 0x01     | OPMODE_CTL_V             | Operation mode volatile control word                 |  |  |  |  |

| USER mem | ory bank - Event logger  | peripheral (volatile, referred to CURRENT_PBA)       |  |  |  |  |

| 0x02     | LTC                      | LTC counter                                          |  |  |  |  |

| 0x03     | LOG_VCOUNT               | Event logger volatile count                          |  |  |  |  |

| 0x04     | LOG_VTSTAMP              | Event logger volatile time-stamp                     |  |  |  |  |

| 0x05     | LOG_VDATA                | Event logger volatile data                           |  |  |  |  |

| USER mem | ory bank - Quality of Se | rvice peripheral (volatile, referred to CURRENT_PBA) |  |  |  |  |

| 0x0F     | QOS_BITS                 | Currently read QoS value of the tag                  |  |  |  |  |

| 0x10     | RESERVED                 | Unspecified tag information                          |  |  |  |  |

| USER mem | ory bank - PWM periphe   | eral (volatile, referred to CURRENT_PBA)             |  |  |  |  |

| 0x11     | PWM_TRIGGER              | PWM trigger                                          |  |  |  |  |

| USER mem | ory bank - GPIO read/w   | rite peripheral (volatile, referred to CURRENT_PBA)  |  |  |  |  |

| 0x12     | GPIO_READ                | Values read from the input GPIO pins                 |  |  |  |  |

| 0x13     | GPIO_WRITE               | Values to write to the output GPIO pins              |  |  |  |  |

| USER mem | ory bank - SPI master m  | nodule (volatile, referred to CURRENT_SBA)           |  |  |  |  |

| 0x00     | SPI MASTER               | Bridge to SPI master module                          |  |  |  |  |

## EPC C1G2

#### **RESERVED MEMORY BANK**

## KILL\_PWD

15 10 7 2 14 13 12 11 9 8 6 5 4 3 1 0

KILL\_PWD\_H

Memory bank: Reserved

Address:  $0 \times 00$ Type: R/W

Factory value: 0x0000

**Description:** Kill password 16 MSB.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

KILL PWD L

Memory bank: Reserved

Address:

0x01

Type:

R/W

Factory value:

0x0000

**Description:** Kill password 16 LSB.

The KILL\_PWD\_H and KILL\_PWD\_L words compose the *Kill password* of the EPC Class-1 Generation-2 tag. The MSB of the password are stored in KILL\_PWD\_H, whereas the LSB are stored in KILL\_PWD\_L.

## ACCESS\_PWD

15 14 13 12 10 9 8 7 5 3 2 1 0 11 6 4

ACCESS PWD H

Memory bank: Reserved

Address:

0x02

Type:

R/W

Factory value:

0x0000

**Description:** Access password 16 MSB.

WWW.FARSENS.COM

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ACCESS PWD L

Memory bank: Reserved

Address: 0x03Type: R/W

**Description:** Access password 16 LSB.

0x0000

The ACCESS\_PWD\_H and ACCESS\_PWD\_L words compose the *Access password* of the EPC Class-1 Generation-2 tag. The MSB of the password are stored in ACCESS\_PWD\_H, whereas the LSB are stored in ACCESS\_PWD\_L.

### SILICON\_REV

Factory value:

7 2 15 14 13 12 10 9 8 6 5 4 3 1 0 11 SILICON REV

Memory bank: Reserved

Address:

0x04

Type:

R

Factory value: 0xFA3X

**Description:** Tag hardware revision identifier.

Silicon revision identifier of the IC.

### CURRENT\_PBA

15 14 13 12 10 9 8 7 6 5 4 3 2 1 0 11 **CURRENT PBA**

Memory bank: Reserved

Address: 0x05 Type: R

Factory value: 0x0080

**Description:** Read-only Peripheral Base Address that is being used by the tag.

This register defines the base address of the peripheral address space. It is preloaded to the default value defined in PER\_BASE\_ADDR.

**CURRENT\_SBA**

7 15 14 13 12 11 10 9 8 6 5 4 3 2 1 0

CURRENT\_SBA

Memory bank: Reserved

Address: 0x06

Type:

Factory value: 0x0100

**Description:** Read-only SPI Base Address that is being used by the tag.

This register defines the base address of the SPI address space. It is preloaded to the default value defined in SPI\_BASE\_ADDR.

# **EPC MEMORY BANK**

### STORED\_CRC

10 9 8 7 6 5 2 1 0 15 14 13 12 11 4 3

### STORED CRC

Memory bank: EPC

Address: 0x00

Type: R

Factory value: N/A

Description: CRC16 value of contents of PC+EPC.

**Description:** CRC16 value of contents of PC+EPC.

Every time the tag is powered up, it operates the CRC16 value of the content of PC+EPC bits. This value is stored in internal volatile registers, and is readable through this register. The STORED\_CRC value is recalculated every time the tag is powered up or soft-rebooted and cannot be overwritten.

## STORED\_PC

| 15            | 14 | 13 | 12 | 11  | 10 | 9 | 8 | 7 | 6 | 5   | 4 | 3 | 2 | 1 | 0 |

|---------------|----|----|----|-----|----|---|---|---|---|-----|---|---|---|---|---|

| EPC_length UM |    |    |    | UMI | ΧI |   |   |   |   | NSI |   |   |   |   |   |

Memory bank: EPC

Address: 0x01Type: R/W

Factory value: 0x3100

**Description:** Protocol-control word.

[15-11] **EPC\_length:** The length of the EPC, in words.

[10] UMI: User memory indicator.

• '0': User memory contains no information

• '1': User memory contains information

[9] XI: XPC W1 indicator.

• '0': XPC\_W1 is not used

• '1': XPC\_W1 is used

[8-0] **NSI:** Numbering system identifier.

If the value written into EPC\_length is not supported by ROCKY100 (it is null or greater than 8), then ROCKY100 will operate as if STORED\_PC was programmed with a value of 0x3500.

Datasheet - DS-ROCKY100-V04 - DECEMBER 2017

#### **EPC**

The EPC\_0, EPC\_1, EPC\_2, EPC\_3, EPC\_4, EPC\_5, EPC\_6 and EPC\_7 words compose the *Electronic Product Code* (EPC) of the EPC Class-1 Generation-2 tag. The MSB of the EPC are stored in EPC\_0, whereas the LSB are stored in EPC\_7.

7 2 15 14 13 12 11 10 9 8 6 5 4 3 1 0 EPC 0 **EPC** Memory bank: 0x02 Address: R/W Type: Factory value: Unique EPC value. Word 0 (MSB) of the EPC. **Description:** 15 14 13 12 11 10 9 7 6 5 4 3 2 1 0 EPC\_1 Memory bank: **EPC** Address: 0x03 R/W Type: Factory value: Unique EPC value. **Description:** Word 1 of the EPC. 15 14 13 12 11 10 9 7 6 5 4 3 2 1 0 EPC 2 **EPC** Memory bank: 0x04 Address: R/W Type: Factory value: Unique EPC value. Word 2 of the EPC. **Description:** 15 7 5 14 13 10 9 6 4 3 2 1 0 12 11 EPC 3

Memory bank: EPC

Address: 0x05

Type: R/W

Factory value: Unique EPC value.

Description: Word 3 of the EPC.

0

2

1

3

14

15

7

6

5

4

11 EPC\_4

10

9

**EPC** Memory bank: Address: 0x06

13

R/W Type:

Factory value: Unique EPC value. Word 4 of the EPC. **Description:**

12

15 14 13 12 7 5 3 2 1 0 11 10 9 8 6 4

EPC\_5

**EPC** Memory bank:

0x07 Address: R/W Type:

Unique EPC value. Factory value: Word 5 of the EPC. **Description:**

7 15 14 13 12 10 9 8 6 5 3 2 1 0 11 4

EPC\_6

**EPC** Memory bank: 0x08 Address: R/W Type:

Unique EPC value. Factory value: Word 6 of the EPC. **Description:**

15 14 13 10 7 1 0 12 11 9 8 6 5 4 3 2

EPC\_7

**EPC** Memory bank: 0x09 Address: R/W Type:

Unique EPC value. Factory value:

Word 7 (LSB) of the EPC. **Description:**

#### **TID MEMORY BANK**

## SHORT TAG TID (CONSTANT)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SHORT TAG TID 0

Memory bank: TID

Address: 0x00

Type: R

Factory value: 0xE282

**Description:** First word of the short tag identification register.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

## SHORT\_TAG\_TID\_1

Memory bank: TID

Address: 0x01

Type: R

Factory value: 0x8001

**Description:** Second word the short tag identification register.

### XTID (CONSTANT)

15 14 13 12 10 9 8 7 6 5 4 3 2 1 0 11

XTID

Memory bank: TID

Address: 0x02

Type:

Factory value: 0x2000

**Description:** Extended Tag Identification.

# SN\_SEG

The SN\_SEG\_0, SN\_SEG\_1 and SN\_SEG\_2 words compose the *Serial number segment* of the TID memory bank. The MSB of the serial number segment are stored in SN\_SEG\_0, whereas the LSB are stored in SN\_SEG\_2.

WWW.FARSENS.COM

Type:

15 14 13 12 11 10 9 7 5 4 3 2 1 0

SN\_SEG\_0

TID Memory bank:

Address: 0x03 R/W

Unique TID value Factory value:

First (MS) word of the serial number segment of the TID memory bank. **Description:**

15 14 13 12 11 10 9 8 7 6 5 3 2 1 0 4

SN\_SEG\_1

TID Memory bank:

0x04 Address: R/W Type:

Unique TID value Factory value:

Second word of the serial number segment of the TID memory bank. Description:

7 15 14 13 12 11 10 9 8 6 5 4 3 2 1 0

SN SEG 2

Memory bank: TID

0x05 Address:

R/W Type:

Unique TID value Factory value:

Last (LS) word of the serial number segment of the TID memory bank. **Description:**

Datasheet - DS-ROCKY100-V04 - DECEMBER 2017

### **USER MEMORY BANK**

The User memory bank of ROCKY100 is mapped to configuration data, user data and peripheral control. The following sections provide a detailed description of the configuration and control registers related to each peripheral.

The user data section can be freely used to store the application data desired by the end user.

#### PERIPHERAL BASE ADDRESS

The base address of the peripheral partition of ROCKY100 is user programable through register PER\_BASE\_ADDR. This means that the mapping of all peripherals described in table 5 is controlled with this register. Although any value can be stored in PER\_BASE\_ADDR, the following restrictions apply to ROCKY100:

- The peripheral base address corresponds with the 14 least significant bits of register PER BASE ADDR.

- The peripheral base address must not fall within the range of the configuration partition of ROCKY100 (memory addresses from 0x00 to 0x2F of the user memory bank).

If the peripheral base address obtained from PER\_BASE\_ADDR is invalid, ROCKY100 will assume a default peripheral base address of 0x0030. Bear in mind that in this circumstance no user data memory will be available to the user.

The actual peripheral base address being use by ROCKY100 can be read from register CURRENT\_PBA at address 0x05 of the reserved memory bank.

#### PERIPHERAL BASE ADDRESS REGISTER

## PERIPHERAL\_BASE\_ADDRESS

| 15  | 14           | 13 | 12  | 11 | 10 | 9 | 8     | 7    | 6     | 5     | 4  | 3 | 2 | 1 | 0 |

|-----|--------------|----|-----|----|----|---|-------|------|-------|-------|----|---|---|---|---|

| R   | FU           |    |     |    |    |   | PERIP | HERA | L_BAS | E_ADI | PR |   |   |   |   |

| Mem | Memory bank: |    | Use | er |    |   |       |      |       |       |    |   |   |   |   |

Address:

0x0D

Type:

R/W

Factory value:

0x0080

**Description:** Peripheral base address register.

[13 - 0] PERIPHERAL BASE ADDR.

#### SPI BASE ADDRESS

The first user memory bank address that is mapped to the SPI Master bridge in ROCKY100 is user configurable through register SPI\_BASE\_ADDR. Although any value can be stored in SPI\_BASE\_ADDR, the following restrictions apply to ROCKY100:

- The SPI base address corresponds with the 15 least significant bits of register SPI BASE ADDR.

- The SPI base address must be at greater than the peripheral base address being used by ROCKY100 (CURRENT\_PBA). This guarantees that the reboot peripheral is always accessible.

If the SPI base address obtained from SPI\_BASE\_ADDR is illegal, ROCKY100 will assume a default SPI base address equal to CURRENT\_PBA plus one. Bear in mind that in this circumstance only the reboot peripheral will be accessible in the memory space of ROCKY100.

The actual SPI base address being use by ROCKY100 can be read from register CURRENT\_SBA at address 0x06 of the reserved memory bank.

#### SPI BASE ADDRESS REGISTER

#### SPI\_BASE\_ADDRESS

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7    | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|----|----|----|----|----|---|-----|------|-------|---|---|---|---|---|---|

| RFU |    |    |    |    |    |   | SPI | BASE | _ADDF | ₹ |   |   |   |   |   |

Memory bank: User

Address: 0x0E

Type: R/W

Factory value: 0x0100

**Description:** SPI base address register.

[14 - 0] **SPI BASE ADDR**.

#### **OPERATION MODE**

ROCKY100 can be configured to operate in different operation modes. Some of those configurations are intended for test purposes, whereas others can be configured to optimize the efficiency of the device for a specific application. Setting these configurations incorrectly can cause the device to stop working. Moreover, it can be interesting for some applications to change some of those configuration only for a single run, so that the original configuration is recovered after resetting the device.

In order to offer all these options, the operation mode configurations can be set by two means: volatile configuration and non-volatile configuration. If the volatile configuration is changed, once the power source is removed the configuration is lost. If the non-volatile configuration is changed, even after a power source cut the configuration will be kept.

The default configuration of ROCKY100 is specified in the non-volatile operation mode control register. If a write operation modifies the contents of the volatile operation mode register, then ROCKY100 will be configured in accordance to this value. In this case, the configuration stored in the non-volatile operation mode control register will be ignored until ROCKY100 is powered down.

| Register      | User memory address | Operation mode control register |  |  |  |  |

|---------------|---------------------|---------------------------------|--|--|--|--|

| OPMODE_CTL_NV | 0x00                | Non-volatile control register   |  |  |  |  |

| OPMODE_CTL_V  | CUR_PBA + 0x01      | Volatile control register       |  |  |  |  |

#### **ASK MODE**

ROCKY100 includes two different ASK demodulators for the forward link: the passive demodulator and the high sensitivity demodulator. The high sensitivity demodulator has a higher power consumption than the passive demodulator. Thus, it is intended to be used in BAP applications. Moreover, the high sensitivity demodulator has a lower saturation input power. In order to cover the complete RF input power range, ROCKY100 has to switch between both demodulators. The behavior of this switching can be configured through the ASKSEL parameter.

| ASKSEL | ASK demodulator selector    |

|--------|-----------------------------|

| '000'  | Passive demodulator         |

| '001'  | High sensitivty demodulator |

| '011'  | Automatic selection         |

The ASK demodulator selector is overrided if any of the GPIOs of ROCKY100 is configured in ASK bypass mode (refer to section GPIO CONFIGURATION in page 44 for further details). If several GPIOs are simultaneously configured in ASK bypass mode, then the GPIO with the highest identifier (GPIO4 in case all GPIOs are configured in this mode) will override the ASK demodulator selector value.

ROCKY100 also allows inverting the output of the selected ASK signal (ASKSEL or GPIO bypass). The ASKPOL parameter allows configuring this feature. In order to use the integrted C1G2 processor, ASKPOL has to be set to '0'.

| ASKPOL | ASK polarity selector                   |

|--------|-----------------------------------------|

| '0'    | ASK follows envelope of RF signal       |

| '1'    | ASK is inverse to envelope of RF signal |

#### **BAP MODE**

ROCKY100 is prepared to be used both in passive and BAP applications. For the latter ones, a dedicated VBAT pin is included. This pin can be connected to VDD by means of an integrated battery switch. This switch is intended to minimize battery drain of BAP tags prior to activation. The switch can be controlled through the BATSW parameter.

| BATSW Battery switch control |                                                  |

|------------------------------|--------------------------------------------------|

| '0'                          | Switch open. Battery supply not connected to VDD |

| '1'                          | Switch closed. Battery supply connected to VDD   |

Moreover, the high sensitivity demodulator may be activated in order to extend the communication range of the device. In such a configuration, a higher current consumption shall be expected. The following configurations are available.

| BAPSENS | Sensitivity | Increment in I <sub>DD</sub> |  |  |

|---------|-------------|------------------------------|--|--|

| '000'   | -24dBm      | -                            |  |  |

| '111'   | -35dBm      | 2 μΑ                         |  |  |

Note that BAPSENS only enables the high sensitivity demodulator. In order to achieve the highest sensitivity values, the ASKSEL parameter should correctly point to the high sensitivity demodulator.

#### **PSK MODE**

The modulation depth of the backscattered signal depends on the PSK modulator. The deeper the modulation is, the higher the SNR of the backward communication link will be under same circumstances. However, the deeper the modulation is, the lower the harvested energy during backscattering will be. Thus, depending on the application, it may be more interesting to increase or decrease the modulation depth.

ROCKY100 allows configuring the modulation depth through the PSKSEL parameter. PSKSEL is a 4 bit parameter. Each bit of PSKSEL can be independently configured. Enabling only the least significant bit of PSKSEL produces the lowest PSK modulation supported by ROCKY100, but maximizes the harvested energy.

| PSKSEL | PSK modulation depth selector |

|--------|-------------------------------|

| '0000' | No modulation                 |

| '0001' | Lowest modulation             |

|        |                               |

| '1000' | Medium modulation             |

|        |                               |

| '1111' | Highest modulation            |

#### **RNG MODE**

The C1G2 core processor requires a Random Number Generator (RNG) for the anti-collision algorithm and data masking. ROCKY100 can be configured to use either a true random number generator or a pseudo random generator. The pseudo random generator requires a seed as starting point. This seed is defined as the value in the TRIM\_C1G2OSC register.

| RNG | Random Number Generation mode |

|-----|-------------------------------|

| '0' | Pseudo-random                 |

| '1' | True random                   |

# C1G2 OSCILLATOR

C1G2 oscillator trimming bits. Sets the internal operation frequency of the digital processor. This value shall be configured so that generated frequency is close to 1.92MHz.

# **ULF OSCILLATOR**

Ultra Low Frequency (ULF) oscillator trimming bits. Sets the internal operation frequency of the Log Time Counter (LTC) time base generator. This value shall be configured so that the generated frequency is close to 1Hz.

#### **OPERATION MODE REGISTERS**

#### OPMODE CTL NV

| 15  | 14 | 13          | 12  | 11 | 10  | 9   | 8 | 7 | 6    | 5  | 4      | 3     | 2  | 1    | 0   |

|-----|----|-------------|-----|----|-----|-----|---|---|------|----|--------|-------|----|------|-----|

| RFU | U  | RST_SESSION | RNG |    | PSK | SEL |   | А | SKSI | EL | ASKPOL | BATSW | BA | APSE | :NS |

Memory bank:

User

Address:

0x00

Type:

R/W

Factory value:

0x1F00

**Description:**

Operation mode volatile control word.

[13] RST\_SESSION: ASK watchdog events reset S0, S2, S3 and SL flags

• '0': reset disabled.

• '1': reset enabled.

[12] **RNG:** random number generator mode.

• '0': pseudo-random mode.

• '1': true random mode.

[11:8] **PSKSEL:** PSK modulation depth selector.

[7:5] **ASKSEL:** ASK source selector.

• '000': Passive demodulator.

• '001': High sensitivity demodulator.

• '011': Automatic selection.

[4] **ASKPOL:** ASK polarity selector.

• '0': ASK follows envelope of RF signal.

• '1': ASK is inverse to envelope of RF signal.

[3] BATSW: Battery switch control.

• '0': switch open. Battery supply not connected to VDD.

• '1': switch closed. Battery supply connected to VDD.

[2:0] **BAPSENS:** communications sensitivity configuration in BAP mode.

• '000': -24dBm.

• '111': -30dBm.

OPMODE\_CTL\_V

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 **RFU RST SESSION ASKPOL BATSW BAPSENS RNG PSKSEL ASKSEL**

Memory bank: User

Address: CUR\_PBA + 0x01 (Default: 0x81)

Type: W

Factory value: 0x00

**Description:** Operation mode volatile control word.

[13] RST\_SESSION: ASK watchdog events reset S0, S2, S3 and SL flags

• '0': reset disabled. • '1': reset enabled.

[12] **RNG:** random number generator mode.

• '0': pseudo-random mode. • '1': true random mode.

[11:8] **PSKSEL:** PSK modulation depth selector.

[7:5] **ASKSEL:** ASK source selector.

• '000': Passive demodulator. • '001': High sensitivity demodulator.

• '011': Automatic selection.

[4] **ASKPOL:** ASK polarity selector.

• '0': ASK follows envelope of RF signal.

• '1': ASK is inverse to envelope of RF signal.

[3] BATSW: Battery switch control.

• '0': switch open. Battery supply not connected to VDD.

• '1': switch closed. Battery supply connected to VDD.

[2:0] **BAPSENS:** communications sensitivity configuration in BAP mode.

• '**000**': -24dBm. • '**111**': -30dBm.

Datasheet - DS-ROCKY100-V04 - DECEMBER 2017

TRIM\_C1G2OSC

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TRIM C1G2OSC

User Memory bank: 0x01 Address:

R/W Type:

0x00 Factory value:

Trimming value for C1G2 oscillator. **Description:**

C1G2 oscillator trimming bits. Sets the internal operation frequency of the digital processor. This value shall be configured so that generated frequency is close to 1.92MHz.

TRIM ULFOSC

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TRIM\_ULFOSC

User Memory bank:

Address: R/W Type:

0x00 Factory value:

Trimming value for ULF oscillator. **Description:**

0x11

# **PSM CONTROL**

The threshold voltages VLOADON, VLOADOFF and the output voltage of VREGL can be set following the next equations:

$$CODE_{dec} = 1183 - 256 \left( \frac{V}{0.6} - 1 \right)$$

(1)

The following table shows three examples of possible VLOAD configuration:

Table 6: VLOAD configuration examples.

|          | Exa | mple 1 | Exa | mple 2 | Example 3 |       |  |

|----------|-----|--------|-----|--------|-----------|-------|--|

|          | ٧   | code   | ٧   | code   | ٧         | code  |  |

| VREGL    | 1.5 | 0x31F  | 2   | 0x249  | 3         | 0x09F |  |

| VLOADON  | 1.7 | 0x2CA  | 2.2 | 0x1F4  | 3.1       | 0x074 |  |

| VLOADOFF | 1.4 | 0x34A  | 1.9 | 0x274  | 2.9       | 0x0CA |  |

Additionally, the output of the voltage monitors used to control startup of the tag and the load can be accessed for Quality of Service purposes. The SPI master module adds this information when triggered. Nevertheless, it is also possible to read the current state of this signals through the QOS\_BITS register.

#### **PSM CONTROL REGISTERS**

#### **PSM CTL**

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 RFU RFU 0 **VREGL MODE GLOAD MODE VLMON EN**

Memory bank: User

Address: 0x02

Type: R/W

Factory value: 0x0000

**Description:** PSM control word.

[6:5] **RFU\_0:** Control word reserved for future use. It must be set to all zeros.

[4:3] **VREGL\_MODE:** VREGL switch mode.

• '00': Off. • '10': Auto.

• '01': On.

[2:1] GLOAD\_MODE: GLOAD switch mode.

• '00': Off. • '10': Auto.

• '01': On. • '11': PWM output.

[0] VLMON\_EN: VLOAD monitor enable.

• '0': Disabled. • '1': Enabled.

# TRIM\_VLON

7 2 15 14 13 12 11 10 9 8 6 4 1 0 RFU TRIM\_VLON

Memory bank: User

Address: 0x03

Type: R/W

Factory value: 0x0174 (2.5V)

**Description:** VLON trimming word.

[9:0] **TRIM\_VLON:** VLOAD ON threshold voltage. Refer to equation 1.

TRIM\_VLOFF

RFU TRIM VLOFF

Memory bank: User

Address: 0x04

Type: R/W

Factory value: 0x029F (1.8V)

**Description:** VLOFF trimming word.

[9:0] TRIM\_VLOFF: VLOAD OFF threshold voltage. Refer to equation 1.

TRIM\_VREGL

RFU TRIM\_VREGL

Memory bank: User

Address: 0x05

Type: R/W

**Factory value:** 0x0249 (2.0V)

**Description:** VREGL trimming word.

[9:0] **TRIM\_VREGL:** VREGL output voltage. Refer to equation 1.

QOS\_BITS

RFU Q3 Q2 Q1 Q0

Memory bank: User

Address: CUR\_PBA + 0x0F (Default: 0x8F)

Type: R

Factory value: 0x00

**Description:** Quality of Service register.

[3]  ${f Q3}$ : VDD is above VLOADON threshold (configured with TRIM\_VLON) .

[2] Q2: VDD is above VLOADOFF threshold (configured with TRIM\_VLOFF).

[1] Q1: VDD is above VTAGON threshold (1.2V).

[0] **Q0:** VDD is above VTAGOFF threshold (0.9V).

# **GPIO**

ROCKY100 includes 5 General Purpose Input Output pins. Each of them can be individually configured to select the desired function. Weak pull (up or down) resistors can be configured in case they are needed.

Additionally, the functionality of the pin has to be mapped to the SPI master, SPI slave, event generator or signal bypass module. For SPI modules, the behavior of each pin is predefined. For events and bypass signals, further configuration is required to select the specific signal. Tables 7 to 10 show the available options.

In case GPIO\_IN is used, then the GPIO is configured as an input and its logical value can be read through register GPIO\_READ. In case GPIO\_OUT is used, then the GPIO is configured as an output and its logical value is set by writing to the GPIO\_WRITE register.

Table 7: SIGSEL definition when **DEVSEL = '10'** (event generator).

| SIGSEL | Event                 | Description                                                                                              |

|--------|-----------------------|----------------------------------------------------------------------------------------------------------|

| 0x00   | command_start         | The tag has started processing a new C1G2 command                                                        |

| 0x01   | command_stop          | The tag has stopped processing a C1G2 command                                                            |

| 0x02   | select_matched        | A valid select command has been received that has asserted the matched flag                              |

| 0x03   | select_mask_matched   | A valid select command with no null mask has been received that has asserted the matched flag            |

| 0x04   | select_unmatched      | A valid select command has been received that has deasserted the matched flag                            |

| 0x05   | select_mask_unmatched | A valid select command has been with no null mask has been received that has deasserted the matched flag |

| 0x07   | null_slot_counter     | The slot counter has a null value after processing a Query, QueryAdjust or QueryRep command              |

| 0x08   | access_UM_NVM         | A memory access to the UM located in NVM has been processed                                              |

| 0x09   | access_UM_config      | A memory access targeted to the configuration registers of the UM bank has been processed                |

| 0x0B   | access_SPI_master     | A memory access targeted to the SPI bridge has been processed                                            |

| 0x0C   | symbol_timeout        | The watchdog in SYMBOL has timed out                                                                     |

| 0x0D   | reboot_or_por         | PoR condition or the control unit of R100 has been rebooted                                              |

| 0x0E   | reboot                | The control unit of R100 has been rebooted                                                               |

| Table 8: SIGSEL definition when <b>DEVSEL = '11'</b> (signal bypass). |                 |           |                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-----------------------------------------------------------------------|-----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SIGSEL                                                                | Signal          | Direction | Description                                                                                                                                                                                                                                                                       |  |  |  |  |

| 0x00                                                                  | GPIO_IN         | Input     | The value read on the pin is copied into GPIO_READ                                                                                                                                                                                                                                |  |  |  |  |

| 0x01                                                                  | GPIO_OUT        | Output    | The value of GPIO_WRITE is copied in the output buffer of the pad                                                                                                                                                                                                                 |  |  |  |  |

| 0x02                                                                  | PWM             | Output    | Output of the PWM generator                                                                                                                                                                                                                                                       |  |  |  |  |

| 0x03                                                                  | EDGE_1_IN       | Input     | Input source to the first edge detector peripheral. If several GPIOs are configured simultaneously in this mode, then the GPIO with the highest identifier (GPIO4, GPIO3,) has preference                                                                                         |  |  |  |  |

| 0x04                                                                  | EDGE_2_IN       | Input     | Input source to the second edge detector peripheral. If several GPIOs are configured simultaneously in this mode, then the GPIO with the highest identifier (GPIO4, GPIO3,) has preference                                                                                        |  |  |  |  |

| 0x05                                                                  | EDGE_1_OUT      | Output    | Outputs the event of the first edge detector peripheral                                                                                                                                                                                                                           |  |  |  |  |

| 0x06                                                                  | EDGE_2_OUT      | Output    | Outputs the event of the second edge detector peripheral                                                                                                                                                                                                                          |  |  |  |  |

| 0x07                                                                  | EVENLOG_MTP     | Output    | On high indicates that the event logger is accessing the MTP memory                                                                                                                                                                                                               |  |  |  |  |

| 0x08                                                                  | SPI_MODE        | Input     | When GPIO4 is configured in this mode, the logical value read from the pad will force an SPI mode on the remaining GPIOs. When GPIO4 = '0', the remaining GPIOs will be configured in SPI master mode. When GPIO4 = '1', the remaining GPIOs will be configured in SPI slave mode |  |  |  |  |

| 0x09                                                                  | SPI_MASTER_CS   | Output    | Outputs the CS signal of the SPI master bridge                                                                                                                                                                                                                                    |  |  |  |  |

| 0x0A                                                                  | SPI_MASTER_SCK  | Output    | Outputs the SCK signal of the SPI master bridge                                                                                                                                                                                                                                   |  |  |  |  |

| 0x0B                                                                  | SPI_MASTER_MOSI | Output    | Outputs the MOSI signal of the SPI master bridge                                                                                                                                                                                                                                  |  |  |  |  |

| 0x0C                                                                  | SPI_MASTER_MISO | Input     | Connects the value read from the GPIO to the MISO port of the SPI master bridge. If several GPIOs are configured simultaneously in this mode, the GPIO with the highest identifier takes preference. GPIO0 in SPI master mode has preference over this configuration              |  |  |  |  |

| 0x0D                                                                  | SPI_SLAVE_CS    | Input     | Connects the value read from the GPIO to the CS port of the SPI slave bridge. If several GPIOs are configured simultaneously in this mode, the GPIO with the highest identifier takes preference. GPIO3 in SPI slave mode has preference over this configuration                  |  |  |  |  |

| 0x0E                                                                  | SPI_SLAVE_SCK   | Input     | Connects the value read from the GPIO to the SCK port of the SPI slave bridge. If several GPIOs are configured simultaneously in this mode, the GPIO with the highest identifier takes preference. GPIO2 in SPI slave mode has preference over this configuration                 |  |  |  |  |

Table 9: SIGSEL definition when **DEVSEL = '11'** (signal bypass) (continued).

| SIGSEL | Signal         | Direction | Description                                                                                                                                                                                                                                                                                                                                  |

|--------|----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0F   | SPI_SLAVE_MOSI | Input     | Connects the value read from the GPIO to the MOSI port of the SPI slave bridge. If several GPIOs are configured simultaneously in this mode, the GPIO with the highest identifier takes preference. GPIO1 in SPI slave mode has preference over this configuration                                                                           |

| 0x10   | SPI_SLAVE_MISO | Output    | Outputs the MISO signal of the SPI slaveter bridge                                                                                                                                                                                                                                                                                           |

| 0x11   | VLOAD_OK       | Output    | On high indicates that the regulated output meets the PSM configuration                                                                                                                                                                                                                                                                      |